## Birla Institute of Technology and Science, Pilani.

Comprehensive Examination: CS/ECE/EEE/INSTR F215: Digital Design

Marks: 40 AY: 2023-24, Semester: I Date: 18-December-2023, Monday Time: 60 minutes CLOSED BOOK Pages:04

| BITS ID: | Name: |

|----------|-------|

|          |       |

| Q1 | Realize the Boolean expression using the minimum number of Transmission Gates (TGs).                    | [5 |

|----|---------------------------------------------------------------------------------------------------------|----|

|    | $F(A, B, C, D) = \sum m(0, 4, 5, 6, 8, 9) + d(10, 11, 12, 13, 14, 15)$ . True and compliment inputs are |    |

|    | available.                                                                                              |    |

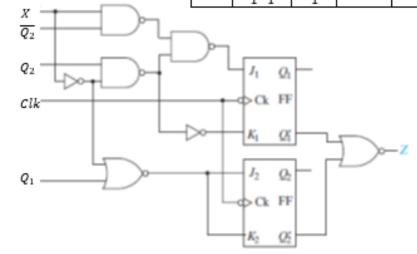

Q2 For the following sequential circuit, construct the state table.

| State | Present<br>State | Input<br>X | Output<br>Z | Flip-flop<br>Input |           | Next State<br>$Q_2^+$ $Q_1^+$ |

|-------|------------------|------------|-------------|--------------------|-----------|-------------------------------|

|       | $Q_2 Q_1$        |            |             | $J_2 K_2$          | $J_1 K_1$ |                               |

| $S_0$ | 0 0              | 0          |             |                    |           |                               |

|       | 0 0              | 1          |             |                    |           |                               |

| $S_1$ | 0 1              | 0          |             |                    |           |                               |

|       | 0 1              | 1          |             |                    |           |                               |

| $S_2$ | 1 0              | 0          |             |                    |           |                               |

|       | 1 0              | 1          |             |                    |           |                               |

| $S_3$ | 1 1              | 0          |             |                    |           |                               |

|       | 1 1              | 1          |             |                    |           |                               |

[5]

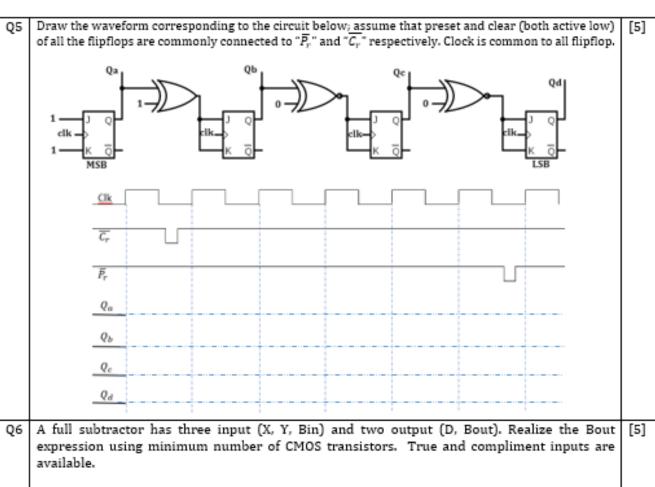

| Q3 | A 4-bit shift register is shown in the figure below. It is clocked, and with each clock pulse, the pattern gets shifted by a one-bit position to the right. |                    |                   |              |             | ern [5]               |          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|--------------|-------------|-----------------------|----------|

|    |                                                                                                                                                             | Clk 1              | 0                 | 0            | 1           |                       |          |

|    |                                                                                                                                                             |                    | , C               |              |             |                       |          |

|    | Assume that the init<br>the following clock p                                                                                                               |                    | registers as 100  | 1. Write the | content of  | the shift registers a | fter     |

|    |                                                                                                                                                             | 1                  | 0                 |              | 0           | 1                     |          |

|    | After 1st clock pulse                                                                                                                                       | e                  |                   |              |             |                       | $\dashv$ |

|    | After 3rd clock puls                                                                                                                                        | e                  |                   |              |             |                       |          |

|    | After 5th clock puls                                                                                                                                        | e                  |                   |              |             |                       |          |

|    | After 7th clock puls                                                                                                                                        | e                  |                   |              |             |                       | $\dashv$ |

|    | To what values sh<br>the first clock puls                                                                                                                   |                    | ster be initializ | ed so that   | the patteri | n (1001) occurs a     | fter     |

|    |                                                                                                                                                             |                    |                   |              |             |                       |          |

| Q4 | Use the following to (multiplier), using Assume $M = -12$                                                                                                   | the booths algorit |                   | n of two ni  | ımbers, M   | (multiplicand) an     | d Q [5]  |

|    | A A                                                                                                                                                         | Q Q                | <b>Q</b> ·1       | С            | ount        | Command               | ]        |

|    | 00000                                                                                                                                                       | 01000              | 0                 |              | -           | Initialization        | 1        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | 1        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | ]        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | +        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | ]        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | -        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | 1        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | 1        |

|    |                                                                                                                                                             |                    |                   |              |             |                       | 1        |

|    |                                                                                                                                                             |                    |                   |              |             |                       |          |

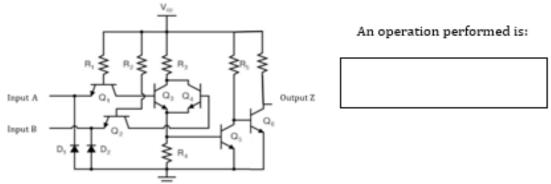

Q7 Identify the logic operation the given circuit performs on input A and input B. Also, complete the following table with respect to the state of the respective transistor (ON or OFF) for the various input combinations.

| Input A | Input B | Q3 | Q4 | Q5 | Q6 | Output Z |

|---------|---------|----|----|----|----|----------|

| 0       | 0       |    |    |    |    |          |

| 0       | 1       |    |    |    |    |          |

| 1       | 0       |    |    |    |    |          |

| 1       | 1       |    |    |    |    |          |

Q8 Complete the partial truth table for the given Verilog code:

module Mini ( input P, Q, Р Q R Q1 Q2 output X, Y assign X = P ^ Q: 0 0 1 assign  $Y = \sim P \& Q$ : 0 1 1 endmodule 0 0 1 module Top ( input P, Q, R, 0 1 0 output Q1, Q2

Mini L0(P, Q, A, B); Mini L1(A, R, Q1, C); assign Q2 = B | <u>C</u>; endmodule

wire A, B, C;

[5]

[5]