# Birla Institute of Technology and Science, Pilani

EEE F341/INSTR F341 Analog Electronics

Second Semester 2021-2022, Comprehensive Exam

## Part A (CLOSED BOOK)

| Time: 85 min | Max. Marks: 50 | Date: 06-05-2022 |

|--------------|----------------|------------------|

| Name:        | ID:            |                  |

Note: Assume all op-amps have  $V_{Sat} = \pm 10$  V, if not mentioned in the question.

## Question no. 1 to 10: Each question carries one mark. $\checkmark$ the correct answer.

| (1) | The other name of voltage follower is<br>(a) Differential amplifier<br>(c) Non-inverting amplifier                                                                                    | <ul><li>(b) Inverting amplifier</li><li>(d) Unity gain amplifier</li></ul>                |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| (2) | A regulated power supply has<br>(a) Error amplifier<br>(c) Feedback network                                                                                                           | <ul><li>(b) Series pass transistor</li><li>(d) All of the above</li></ul>                 |

| (3) | A general second order filter has roll-off rate<br>(a) -20 dB/decade<br>(c) -40 dB/decade                                                                                             | (b) -10 dB/decade<br>(d) -30 dB/decade                                                    |

| (4) | Select correct statement of PLL<br>(a) Capture range smaller than lock range<br>(c) Capture range is equal to lock range                                                              | <ul><li>(b) Lock range smaller than capture range</li><li>(d) None of the above</li></ul> |

| (5) | In PLL, name of phase detector is<br>(a) Adder<br>(c) Multiplier                                                                                                                      | <ul><li>(b) Subtractor</li><li>(d) Divider</li></ul>                                      |

| (6) | The gain of an op-amp decreases at high frequency due to(a) Capacitance(b) Resistance(c) Gain(d) None of the above                                                                    |                                                                                           |

| (7) | VCO is designed so that at zero voltage it is oscillating at some initial frequency called(a) Cut-off frequency(b) Free-cycle frequency(c) Corner frequency(d) Free-running frequency |                                                                                           |

| (8) | Find the maximum frequency for a sine output voltage of 10 V peak with op-amp whose slew rate is 1 V/µs<br>(a) 16 kHz (b) 15 kHz<br>(c) 14 kHz (d) 12 kHz                             |                                                                                           |

| (9) | Gain of differentiator using op-amp is<br>(a) $\omega R_f C_1$<br>(c) $-j\omega R_f C_1$                                                                                              | (b) $\omega/R_f C_1$<br>(d) $1/\omega R_f C_1$                                            |

(10) A second order filter has two poles at  $s = -0.5 \pm j0.866$  and transmission zero at 2 rad/s. What is the correct transfer function for unity gain at dc.

[2]

| (a) $\frac{S^2+4}{S^2+S+1}$                           | (b) $\frac{1}{4} \frac{S^2 + 4}{S^2 + S + 1}$ |

|-------------------------------------------------------|-----------------------------------------------|

| (c) $\frac{\frac{S^{2}+S+1}{S}}{\frac{S^{2}+S+1}{S}}$ | (d) $\frac{4}{\frac{S+2}{S+2}}$               |

#### Question no. 11 to 25: Write correct answer(s) in the blanks.

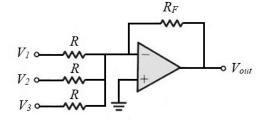

(11) In the given circuit consider the inputs like  $V_1 =$ +2 V,  $V_2 =$  +3 V,  $V_3 =$  +4 V,  $R_F = R = 1 \text{ k}\Omega$  and supply voltage ±15 V. Determine output voltage.

V<sub>out</sub> = \_\_\_\_\_ V

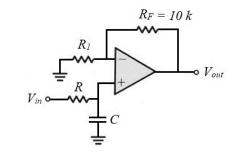

- (12) For the given filter circuit cut-off frequency is 2 kHz, pass band gain 2 and C=0.01 μF.

Find,

- $R = \underline{\qquad } k\Omega \qquad [2]$   $R_1 = \underline{\qquad } k\Omega \qquad [1]$

- (13) Determine the voltage gain (A<sub>f</sub>), input resistance (R<sub>if</sub>) and output resistance (R<sub>of</sub>) with feedback for voltage-series feedback amplifier having A= -100 (V/V), R<sub>i</sub> = 10 k $\Omega$ , and R<sub>0</sub>=20 k $\Omega$  for feedback factor  $\beta$  = -0.5.

$A_{f} =$ \_\_\_\_\_(V/V) [1]

$R_{if} = \underline{\qquad} k\Omega \qquad [1]$

$R_{\rm of} = \underline{\qquad} \Omega \qquad [1]$

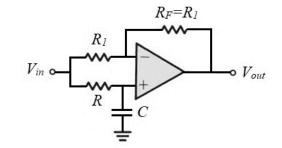

(14) Determine the phase angle ( $\theta$ ) and time delay ( $t_d$ ) for the circuit given for a frequency of 2 kHz, assuming R<sub>1</sub>=20 k $\Omega$ , R= 39 k $\Omega$ , R<sub>F</sub>=R<sub>1</sub> and C=1 nF.

$\theta =$  [2]

$t_d = \____ \mu s$  [1]

(15) A first order low pass Butterworth active filter has a cut-off frequency of 10 kHz and unity gain at low frequency. Find the voltage transfer function magnitude in dB at 12 kHz for the filter. (Consider  $\varepsilon$ =1)

$|H(j\omega)| = \underline{\qquad} dB \qquad [2]$

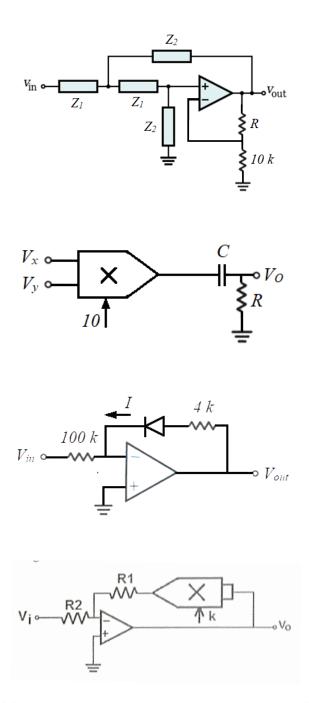

(16) Design the Sallen-Key VCVS second order High Pass Butterworth filter to have 3 dB cutoff frequency of 20 kHz. Use capacitance of 1.59 nF only. Find,

$$Z_1 =$$

[1]

$$Z_2 =$$

\_\_\_\_\_[1]

(17) For the circuit given below find the expression for V<sub>0</sub> assuming large value of capacitor. Given,  $V_x = 4 Sin(1000\pi t)$  V  $V_x = 4 Sin(1000\pi t + 20^\circ)$  V

$$V_y = 4Sin(1000\pi t + 30^\circ)$$

V

V<sub>0</sub> = \_\_\_\_\_V [2]

(18) Calculate I and V<sub>out</sub> of the given circuit where, V<sub>in</sub>= -1 V, reverse saturation current (I<sub>S</sub>) = 1  $\mu$ A and thermal voltage (V<sub>T</sub>) = 26 mV. (Consider,  $\eta$ =1 for Si diode)

Current (I): \_\_\_\_\_ µA [1]

- V<sub>out</sub>: \_\_\_\_\_ V [2]

- (19) Find  $V_0$  expression for the given circuit.

V<sub>0</sub>=\_\_\_\_\_[2]

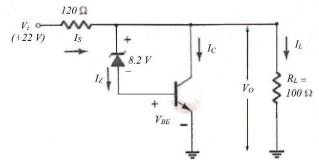

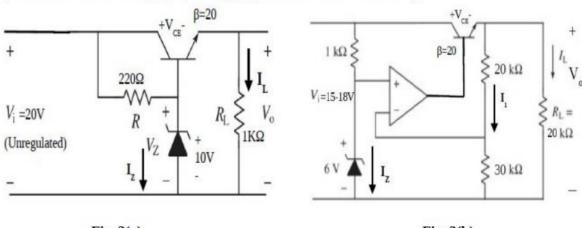

- (20) For the given voltage regulator circuit consider base-emitter voltage as 0.7 V. Find,

- Vo = \_\_\_\_\_ V

- I<sub>S</sub> = \_\_\_\_\_ A

- I<sub>C</sub> = \_\_\_\_\_ mA

[2]

[1]

[1]

(21) For an isolation amplifier,  $C_{ISO} = 2.2$  pF, IMRR = 180 dB,  $V_{ISO}=1000$  V and input signal frequency 20 MHz. Find

Impedance across isolation barrier: \_\_\_\_\_  $k\Omega$  [1]

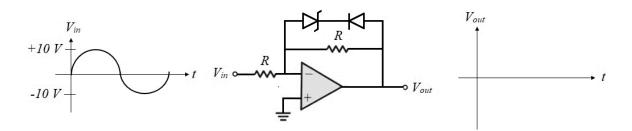

(22) Sketch and label V<sub>out</sub> for the given circuit. Consider Zener drop 3.3 V and forward diode drop 0.7 V. For op-amp  $\pm V_{sat} = \pm 12$  V. [2]

(23) For the given clamping circuit, assume  $V_{ref} = 1.5$ V and input voltage varies from -2.5 V to 5 V Find  $V_C$ : \_\_\_\_\_\_ V [1]

Peak value of  $V_{out}$ :\_\_\_\_\_V [1]

Maximum differential input voltage of op-amp: \_\_\_\_\_\_V [1]

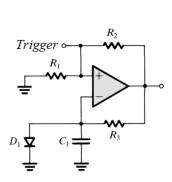

- (24) Write the expression of the pulse width (T) for the given monostable multivibrator when  $V_{sat} \gg$  forward diode drop (V<sub>D</sub>) and R<sub>1</sub>=R<sub>2</sub>.

- T = \_\_\_\_\_ [2]

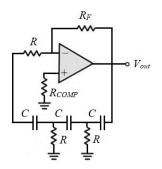

- (25) For the given RC phase shift oscillator  $f_0=300$  Hz. (Consider C = 0.1  $\mu$ F)

### Find,

Input resistance = \_\_\_\_\_  $k\Omega$  [2]

$R_F = \_$  k $\Omega$  [1]

-----END------

•  $V_{out}$

## **Birla Institute of Technology and Science, Pilani**

EEE F341/INSTR F341 Analog Electronics

Second Semester 2021-2022, Comprehensive Exam

Part B (OPEN BOOK) Max. Marks: 55

### Time: 95 min

Note: Assume all op-amps have  $V_{Sat}$ = ± 10 V, if not mentioned in the question.

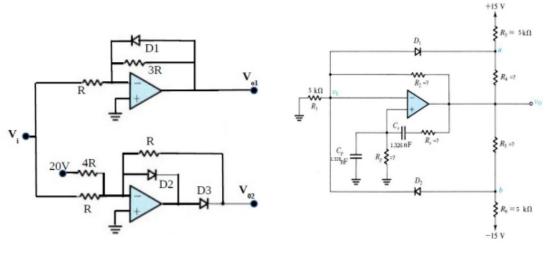

**Q1.** For the given precision circuit shown in Fig 1, now, draw the transfer characteristics i.e  $V_{o1}$  vs  $V_i$  and  $V_{o2}$  vs  $V_i$ . Consider forward diode drop of 0.7V for  $D_1$ ,  $D_2$ , and  $D_3$ . **[6M]**

**Q2.** Design the oscillator circuit shown in Fig.2 to sustain oscillation at 10KHz frequency with  $\pm$  6V output. Consider, forward diode drop as 0.7V. Find R<sub>P</sub>,R<sub>s</sub> R<sub>2</sub>, R<sub>4</sub>, R<sub>5</sub>. [8M]

Fig. 1

Date: 06-05-2022

**Q3.** For the voltage regulator circuits as shown in Fig. 3(a,b). Consider  $V_{BE} = 0.7V$ . [12M] a). Find out the value of  $V_0$ ,  $V_{CE}$ ,  $I_L$  and  $I_Z$  for circuit shown in fig3a.

b). Find out the value of V<sub>o</sub>, I<sub>1</sub>, I<sub>L</sub> and P<sub>dmax</sub> by BJT for circuit shown in fig3b.

Fig. 3(a)

Fig. 3(b)

**P.T.O**

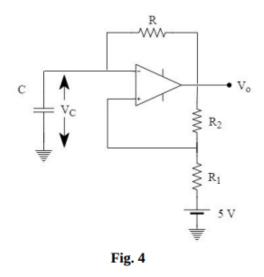

**Q4.** For the wave generator circuit shown in Fig. 4, find the expression of  $T_H$ ,  $T_L$  and frequency (f) in form of RC. If,  $C = 0.1 \mu F$  and  $R = 22.62 k \Omega$ , then draw and label  $V_o$  and  $V_c$ . ( $\pm Vsat = \pm 15V$  and  $R_2 = 9R_1$ ).

[12M]

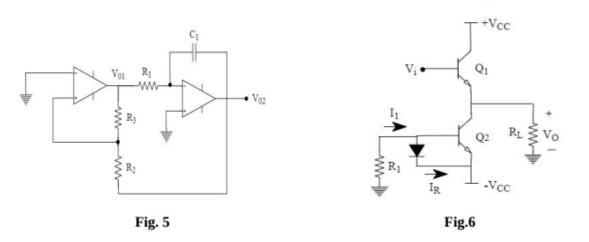

**Q5.** For the circuit shown in Fig. 5, comment on the type of waveform to be produced at  $V_{01}$  and  $V_{o2}$ . Determine the period, frequency and peak value of the signal at  $V_{o1}$  and  $V_{o2}$ . Also, sketch and label the  $V_{o1}$  and  $V_{o2}$  waveforms. Consider  $R_1 = 100k\Omega$ ,  $R_2 = 10k\Omega$ ,  $R_3 = 20k\Omega$ ,  $C_1 = 0.01\mu$ F and  $\pm V_{sat} = \pm 14V$ . [8M]

**Q6.** Design the emitter follower circuit shown in Fig. 6. Assume  $V_{cc} = 12V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEsat} = 0.5V$ ,  $I_R = 5mA$  and  $R_L = 650\Omega$ .

a) Determine the critical value of load resistance to avoid distortion.

**b)** Calculate peak to peak output voltage swing if  $R_L = 650\Omega$ .

c) Also, calculate peak-to-peak output voltage swing and power efficiency ( $\eta$ ) if R<sub>L</sub> = 2.5K $\Omega$ .

----- END------

[9M]