## Birla Institute of Technology and Science, Pilani

EEE G594, Advanced VLSI Devices

Comprehensive Examination, I Semester 2017-2018

## Part A: CLOSED BOOK

Time: 2 hMax. Marks=70Date: 02-12-2017[Given:  $\varepsilon_{Si} = 11.9$ ,  $\varepsilon_{ox} = 3.9$ ,  $\varepsilon_0 = 8.85 \times 10^{-12}$  F/m,  $n_i(Si) = 1.5 \times 10^{10}$  cm<sup>-3</sup>,  $E_g(Si)=1.12$  eV,  $q=1.6 \times 10^{-19}$ C,  $k=1.38 \times 10^{-23}$  m<sup>2</sup>kgs<sup>-2</sup>k<sup>-1</sup>, T=300 K,  $\mu_n=450$  cm<sup>2</sup>/V-s,  $\mu_p=250$  cm<sup>2</sup>/V-s]

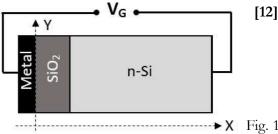

- [1] Fig. 1 shows a M-I-S junction applied  $V_G$  voltage. Draw and label the distribution of following quantities for (i)  $V_G$  at  $V_T$  and (ii)  $V_G$  beyond  $V_T$ . [12]

- (a) Charge  $[\varrho(x)]$

- (b) Electric field [E(x)]

- (c) Potential  $[\psi(x)]$

- [2] Consider a long channel n-MOSFET with gate width near source end is W and drain end is W+(L/a) where, L is the channel length and a (>1) is a constant. Derive a drain current expression in liner and saturation region considering gradual channel approximation approach (μ<sub>n</sub>: Channel Mobility & C<sub>ox</sub>: Oxide capacitance).

- [3] Derive an expression of electronic potential [φ(x,y)] in channel region of a fully depleted symmetric quadruple gate MOSFET considering required boundary conditions. Also derive the expression of natural length (λ) of the device from φ(x,y) expression.

- [4] (a) How electrostatic integrity (EI) varies for Bulk, FD and DG MOSFETs?

(b) How the SCE is controlled with increase of number of gate in MOSFET?

(c) What are the advantages and disadvantages of BCE and ES inverted staggered TFTs?

- [5] (a) For an ultrathin body (t<sub>si</sub><10 nm) DG n-MOSFET, derive the expression for channel potential considering volume inversion effect. What will be the possible change of V<sub>T</sub> when t<sub>si</sub><<10 nm.</li>

(b) Describe the structural confinement (SC) and electrical confinement (EC) for FinFET? If, body doping of a FinFET increases, what confinement will be increased/decreased and why?

- [6] (a) What are the origin of parasitic resistances and capacitance in FinFET source drain region (use suitable diagram)?(b) In a double gate n-channel FinFET, source and drain region have been replaced by SiC instead of Si. What performance improvement would be found and why (use suitable diagram)?

[4+4=8]

[7] (a) How the FDSOI MOSFET reduces the static power consumption of VLSI circuit?

(b) For a SOI MOSFET, N<sub>A</sub>=2×10<sup>17</sup> cm<sup>-3</sup>, t<sub>OX</sub>=10 nm, t<sub>BOX</sub>= 25 nm and t<sub>Si</sub>= 90 nm. What is the body factor (n) of the device? If, t<sub>Si</sub> reduces from 90 nm to 60 nm, what will be the new body factor (n) of the device. What is the improvement in subthreshold swing for the reduction of t<sub>Si</sub>.

[4+8=12]

## Birla Institute of Technology and Science, Pilani

EEE G594, Advanced VLSI Devices Comprehensive Examination, I Semester 2017-2018

|           | Part B: OPEN BOOK |                  |

|-----------|-------------------|------------------|

| Time: 1 h | Max. Marks=35     | Date: 02-12-2017 |

[Given:  $\varepsilon_{Si} = 11.9$ ,  $\varepsilon_{ox} = 3.9$ ,  $\varepsilon_0 = 8.85 \times 10^{-12} \text{ F/m}$ ,  $n_i(Si) = 1.5 \times 10^{10} \text{ cm}^{-3}$ ,  $E_g(Si)=1.12 \text{ eV}$ ,  $q=1.6 \times 10^{-19} \text{ C}$ ,  $k=1.38 \times 10^{-23} \text{ m}^2 \text{kgs}^{-2} \text{k}^{-1}$ , T=300 K,  $\mu_n=450 \text{ cm}^2/\text{V-s}$ ,  $\mu_p=250 \text{ cm}^2/\text{V-s}$ ]

- Consider an M-I-S capacitor fabricated on a p-type silicon substrate which is doped with a net acceptor concentration N<sub>A</sub> of 2×10<sup>16</sup> cm<sup>-3</sup>. The electrostatic potential of the gate metal relative to intrinsic silicon is +0.3 V and the gate dielectric is silicon dioxide of 25 nm thick. Calculate the depletion charge Q<sub>d</sub>, inversion charge Q<sub>i</sub> and sheet charge density in the inversion layer when the gate voltage is 2 V greater than the threshold voltage? [12]

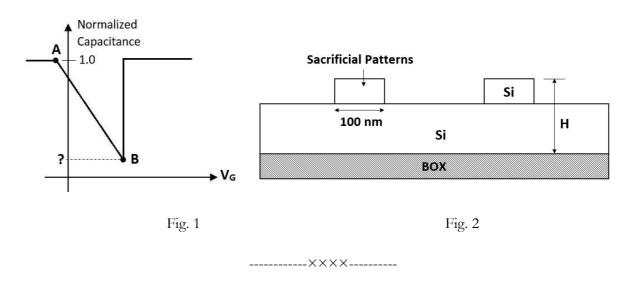

- [2] Fig. 1 shows a characteristics of normalized capacitance vs gate voltage (V<sub>G</sub>) for a Metal/SiO<sub>2</sub>/p-Si junction. If, the doping of p-Si is 5×10<sup>16</sup> cm<sup>-3</sup> and oxide thickness is 100 nm what is the value of normalized capacitance at point B.

- [3] Fig. 2 shows a sacrificial pattern formed by optical photolithography where P<sub>FIN</sub> is 300 nm. Two step spacer defined fin formation process is applied to develop SOI FinFET. In both the steps, spacer width will be the half of sacrificial pattern width. In both the process steps, anisotropic etching time was same. [16]

- (a) Draw the schematic of all the process steps.

- (b) For tri-gate SOI FinFET formation, what will be the fin height when 40<sup>o</sup> tilt-angle required for S/D implant.

- (c) What will be the Si wafer height (H) for the complete process steps?

- (d) For double-gate SOI FinFET with same fin height in (b), what will be the hark mask height when 35<sup>o</sup> tilt-angle required for S/D implant.