TIME-3 hrs.

## TOTAL 5 QUESTIONS

NOTE: State your assumptions clearly

- ✓ Answers should be clear, concise and legible. Specify your assumptions clearly. Do all parts of same question together. Diagrams should be neat and labeled properly. NO MARKS for unnecessary theoretical explanation.

- ✓ Although your answers are important, your REASONS for giving those answers are even more important. Please, explain what you are doing and why. So, justify your answers

*Given ginv=1, pinv=1, for standard CMOS inverter.*

*Common data*: Use the following common data <u>if not mentioned specifically</u> in the question

For 0.25µm Technology node --

- Take Vdd=2.5 V, |Vtn| = |Vtp| = 0.5V,  $W_{min} = L_{min} = 0.5$  um,  $\Upsilon = 0$ ,  $u_n Cox = 120 uA/V^2$ ,  $u_p Cox = 60 uA/V^2$ ,

- Velocity of electromagnetic wave in wire = 15 cm/nsec

- On-resistances of NMOS and PMOS transistors equals [20 k  $\Omega$ / (*W*/*L*)] and [40 k  $\Omega$ /(*W*/*L*)], respectively

- Clock signal has 50 % duty cycle.

- Wire resistance per unit length (for wire width=1um)=0.05ohm/ um, Wire capacitance per unit length (for wire width=1um)= 2 femto F/um

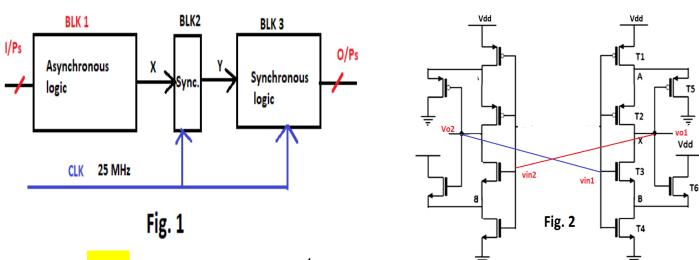

Q1. Consider Fig. 1. Given signal rise time  $t_{rise} = 20nS$

- Blk-1 is a 4-phase pipeline with 'done' signal with maximum cycle time =  $1 \mu$  sec

- Blk-2 is a 4-stage cascaded synchronizer.

- Blk-3 is positive edge triggered clocked pipeline, with Clk frequency = 25 MHz

- D-FF has Tsetup= Thold= Tc-q = 5 n-sec,

- Bi-stable element (cross coupled inverter) has time constant- =  $\tau$  = 4nano Sec

- a) Determine Mean time between failure (MTBF) of BLK-2 (in years).

- b) Re-estimate MTBF of BLK-2 If clk has a positive skew of 100 pS in Fig. 2, (in years).

- c) Re-estimate MTBF of BLK-2, If only first two stages of Blk-2 are operated with frequency of Blk-1 in Fig. 2 (in years).

- d) In part (a), the bistable element of each stage is replaced by cross coupled Schmitt trigger circuit. (Fig. 2). It has upper threshold = 1V and lower threshold =  $0.5V \cdot \tau = 5nS$ . Re-estimate MTBF (in years).

(PTO)

## [ 8 marks]

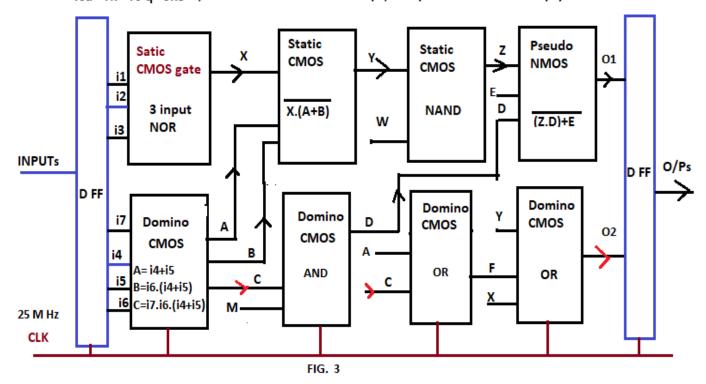

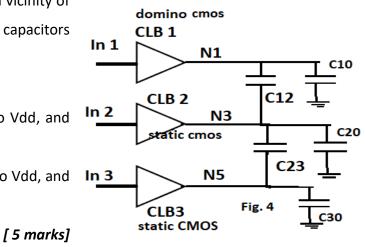

- **Q2.** For BLK-1 in Fig. 1-- the synchronous logic design of BLK 1 is shown in Fig. 3. Assume 1 Cg= W<sub>min</sub> L<sub>min</sub> Cox

- a) Sketch and lable the entire schematic of longest CLB data path/s i.e (i1, i2----i7 to O1/O2).

- b) Determine logical effort of each stage in part (a) in each data path/s

- c) Hence determine path effort 'F' of each data path/s

- d) Determine the minimum delay of path consisting of domino gates without changing number of stages. In the path.

[ 10 marks]

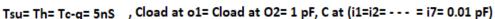

Q3. Consider Fig. 4 with nodes N1, N2, N3 are in vicinity of each other. Given C10=C20=C30, and coupling capacitors C23=C12= (0.25)C20,

Determine the max. voltage level ----

- a) at node N3 if node N3 is initially charged to Vdd, and then only N5 switches from Vdd to 0.

- b) at node N1 if node N1 is initially precharged to Vdd, and then both N3, and N5 switches from Vdd to 0.

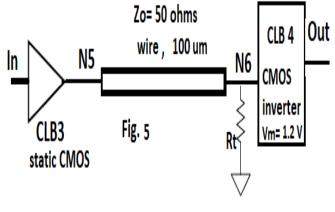

Q4. Consider Fig. 5, showing a data paths on an IC operating at 1 G Hz.

Each wire / trace is 100 um long with 20 nano-H inductance , 2 nano-F capacitance),

## Assume loss less behavior.

- a) Determine termination resistance (Rt) required at nodes (N6) for incidence wave switching. Assume Rout of CLB3 is 50 ohms

- b) Now, impedances at nodes N5, and N6 changes to 60 ohms due to PVT variations . Hence, Sketch and label the lattice diagram for (rising step) signal propagation through wire.. Now find the total propagation delay from N5 to N6. Assume C6= 0.1 pF is the input capacitance of CLB4

## [6 marks]

- Q5. Answer the following with proper justification/ calculation----

- a) Consider wire (N5 to N6) in Fig. 5, having length 100 um long with 20 nano H inductance, 2 nano F

*capacitance*), Determine the propagation delay through wire using distributed RC approach.

- b) Sketch and label segmented break before make pulse transmitter driver for Fig. 5

- c) In Fig. 5, for incidence wave switching , design thevenin termination resistance (Rt) and termination voltage Vt required at nodes (N6).

- d) In Fig 3, determine optimum number of stages for data path consisting of only static cmos gates..

- e) Now in Fig. 4, determine the net capacitive load appearing at node N3, if N1 switches from 0 to Vdd, and node N3 switches from Vdd to 0. (*hint--- use principle of superposition*)

[10 marks]

-----END------END------