# **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

COMPREHENSIVE EXAMINATION

#### Semester I: 2022-2023 Part A: Closed Book

# MEL G631: Physics and Modelling of Microelectronic Devices

Date: 27/12/2022 Maximum Marks: **35** Maximum Time: 75 minutes \_\_\_\_\_ Given (Use, if not specified in the questions): q=1.6×10<sup>-19</sup> C, k=1.38×10<sup>-23</sup> m<sup>2</sup>kgs<sup>-2</sup>k<sup>-1</sup>, T=300 K, kT/q=0.026 V,  $\epsilon_0$ =8.85×10<sup>-14</sup> F/cm Si:  $\epsilon_r = 11.8$ ,  $n_i = 1.45 \times 10^{10}$  cm<sup>-3</sup>,  $E_g = 1.12$  eV,  $\mu_n = 1300$  cm<sup>2</sup>/V-s,  $\mu_p(Si) = 480$  cm<sup>2</sup>/V-s,  $q\chi = 4.05$  eV,  $N_{C}=2.8\times10^{19}$  cm<sup>-3</sup>,  $N_{V}=1.04\times10^{19}$  cm<sup>-3</sup>. **Au**:  $\phi_{\rm M} = 4.75 \text{ eV}$ -----Answer should be very brief and to the point. Q1. Where is the probability of finding of an electron is exactly half  $(\frac{1}{2})$ ? [1] Ans: O2. Suppose, the probability of occupancy by an electron in conduction band is represented by [1]  $f_D(E)$ . How can we represent the probability of occupancy by a hole in valance band? Ans: Q3. If,  $E_C - E_F \gg kT$ , write the Fermi function using Maxwell-Boltzmann's distribution. [1] Ans: What do you mean by the charge neutrality in a doped semiconductor? Explain with a Q4. [2] suitable expression. Ans:

Q5 If the effective mass of electron  $(m_n^*)$  in Si crystal is  $0.3m_0$ , find the thermal velocity  $(V_{th})$  [2] of electron in the same crystal at 300 k.

Ans:

Q6. What is the reason behind the lowering of metal work function in a MS junction under [2] high field application?

Ans:

Q7. What are the criteria for constructing a metal-semiconductor non-rectifying (Ohmic) [2] contact?

Ans:

Q8. How can you define radiative and non-radiative semiconductors? Provide examples for [2] both type of semiconductors.

Ans:

Q9. What is the difference between band to band and Auger recombination for low level [2] injection? Write the expression of carrier life time for both the cases.

Ans:

Q10. Write the expression of multiplication factor in avalanche breakdown and what is the [2] condition for unlimited multiplication?

Ans:

Q11. Why is the reason to maintain equilibrium in semiconductor of a MOS junction under [2] biasing condition?

Ans:

- Q12. Draw and label a Q-V characteristic Ans: of an ideal MOS junction where ntype Si is used as the semiconductor. Indicate the operating conditions i.e. accumulation, depletion and inversion.

- Q13. Draw a schematic of a parasitic Ans: bipolar transistor formation in an n-MOSFET due to impact ionization effect. Also, show the direction of the flow of electron and hole.

- Q14. Draw an energy band diagram of a Ans: short channel n-MOSFET to show the drain induced barrier lowering (DIBL).

[2]

[2]

[2]

[2]

- Q16. A small negative voltage is applied to the bulk terminal of a MOSFET (w.r.t the source). [2] Tick the correct answer

- Depletion charge (in channel): Increase/Decrease

- Inversion change (in channel): Increase/Decrease

- Threshold voltage: Increase/Decrease

- Q17. Consider 's' is the scaling factor. For, constant field scaling, write the appropriate scaled parameters. Example: Gate length (L): L/s

- Doping  $(N_A)$ :

- Propagation delay (τ):

- Power delay product (P.τ):

- Depletion width (W<sub>D</sub>):

- Q18. Consider a chrome-silicon metal-semiconductor junction where work function of [4] chromium is 4.5 eV and donor doping of silicon is 10<sup>17</sup> cm<sup>-3</sup>.

- (a) Calculate the barrier height Ans:

- (b) Built-in potential Ans:

If, 5 V reverse bias voltage is applied to the junction, calculate

- (c) Depletion layer width Ans:

- (d) Electric field in the semiconductor at the interface Ans:

- (e) Potential at half of the depletion width Ans:

- (f) Capacitance per unit area Ans:

-----End-----

[2]

## **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

COMPREHENSIVE EXAMINATION

Semester I: 2022-2023

#### Part B: Open Book

MEL G631: Physics and Modelling of Microelectronic Devices

Date: 27/12/2022

Maximum Marks: 45

Maximum Time: 105 minutes

Given (Use, if not specified in the questions):

$q=1.6 \times 10^{-19}$  C,  $k=1.38 \times 10^{-23}$  m<sup>2</sup>kgs<sup>-2</sup>k<sup>-1</sup>, T=300 K, kT/q=0.026 V,  $\epsilon_0=8.85 \times 10^{-14}$  F/cm

Si:  $\epsilon_r=11.8$ ,  $n_i=1.45 \times 10^{10}$  cm<sup>-3</sup>,  $E_g=1.12$  eV,  $\mu_n=1300$  cm<sup>2</sup>/V-s,  $\mu_p(Si)=480$  cm<sup>2</sup>/V-s,  $q\chi=4.05$  eV,  $N_C=2.8 \times 10^{19}$  cm<sup>-3</sup>,  $N_V=1.04 \times 10^{19}$  cm<sup>-3</sup>.

Au:  $\phi_M = 4.75$  eV

Attempt all the questions.

**Q1.** In a given n-p junction donor and acceptor concentrations are  $1.45 \times 10^{17}$  cm<sup>-3</sup> and  $1.45 \times 10^{16}$  cm<sup>-3</sup>, respectively. Consider, room temperature (300 k),  $\mu_n = 1300$  cm<sup>2</sup>/V-s,  $\mu_p = 480$  cm<sup>2</sup>/V-s,  $\tau_n = \tau_p = 1$  µs.

Also consider the physical thickness of n and p both the side as 100 µm.

- (a) Sketch and label majority and minority carrier concentrations under 0.6 V forward bias. Also find the value of injected minority carriers at the boundary for both the side. [4]

- (b) Calculate I<sub>n</sub>(x<sub>p</sub>), I<sub>p</sub>(-x<sub>n</sub>) and total current (I) at 0.6 forward bias. Consider cross sectional area of the np junction as 10<sup>-4</sup> cm<sup>2</sup>.

[3]

- (c) Repeat part (a) and calculate I<sub>n</sub>(x<sub>p</sub>), I<sub>p</sub>(-x<sub>n</sub>) and total current (I) for the physical thickness of n and p both the side as 1 μm.

- (d) What is the change in total current for 1  $\mu$ m device as compared to the 100  $\mu$ m device? [1]

- (e) What is the average electron and hole carrier life time of the minority carrier in 1 µm device? [1]

### Q2

(a). For an n-channel MOSFET derive the following expression for the channel voltage [V(y)] at the edge of saturation (i.e. pinch off). [6]

$$V(y) = (V_{GS} - V_T) \left( 1 - \sqrt{1 - \frac{y}{L}} \right)$$

Where, L is the channel length (or gate length); source end as y = 0 and drain end as y = L. (Hint: *Use I<sub>DS</sub>=I<sub>DSAT</sub>, ignore velocity saturation*)

(b). Consider a long channel n-MOSFET with gate width near source end is W and drain end is  $W+(L/\alpha)$  where, L is the channel length and  $\alpha$  (>1) is a constant. Derive a drain current expression in linear and saturation region considering gradual channel approximation approach. (Consider:  $\mu_n$ : Constant mobility and Cox: Oxide capacitance). [5]

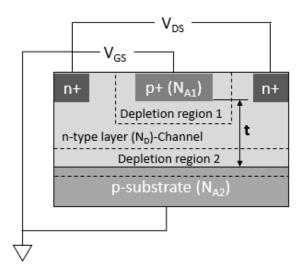

**Q3.** A schematic of junction filed effect transistor is shown in the figure below. Consider W and L are the width and length of the device. Derive a drain current expression for very small  $V_{DS}$ . [5]

**Q4.** Consider a n–channel n<sup>+</sup> poly-SiO<sub>2</sub>-Si MOSFET with gate oxide thickness ( $t_{ox}$ ) = 5 nm, channel length (L) = 0.6 µm and acceptor density (N<sub>A</sub>) = 2×10<sup>17</sup> cm<sup>-3</sup>. Calculate V<sub>DSAT</sub> value with and without gradual channel approximation considering flat band voltage (V<sub>FB</sub>) as -1.1 V, V<sub>GS</sub> = 2 V and bulk to source voltage (V<sub>BS</sub>) as zero. Again calculate the V<sub>DSAT</sub> considering velocity saturation where saturated velocity of electron at room temperature (V<sub>S</sub>) is 10<sup>7</sup> cm/s and electron mobility  $\mu_n = 450 \text{ cm}^2/\text{V-s}$ . [7]

**Q5.** Consider a n–channel n<sup>+</sup> poly-SiO<sub>2</sub>-Si MOSFET with gate oxide thickness ( $t_{ox}$ ) = 5 nm, channel length (L) = 180 nm and width (W) = 324 nm, acceptor impurity ( $N_A$ ) = 2×10<sup>17</sup> cm<sup>-3</sup> and number of fixed oxide charge 4.92×10<sup>11</sup> cm<sup>-2</sup>. Calculate [7]

\_\_\_\_\_

- (a) Threshold voltage

- (b) Surface potential at  $V_{GS} = -334 \text{ mV}$

- (c) Calculate drain current at  $V_{GS}$ = -334 mV considering  $V_{DS}$  = 0.5 V and  $\mu_n$  = 500 cm<sup>2</sup>/V-s.