## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI COMPREHENSIVE EXAMINATION Semester I: 2023-2024 Part A: Closed Book MEL G631: Physics and Modelling of Microelectronic Devices

| Date: 08/12/2022                                                                                                                                                                                                                                                                                                                                                           | Maximum Marks: 40                                                                                                                          | Maximum Time: 90 minutes   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Given (Use, if not specified in the quadratic q=1.6×10 <sup>-19</sup> C, k=1.38×10 <sup>-23</sup> m <sup>2</sup> kgs <sup>-1</sup><br>Si: $\varepsilon_r$ =11.8, n <sub>i</sub> =1.45×10 <sup>10</sup> cm <sup>-3</sup> , Eg=1<br>N <sub>C</sub> =2.8×10 <sup>19</sup> cm <sup>-3</sup> , N <sub>V</sub> =1.04×10 <sup>19</sup> cm <sup>-1</sup><br>Au: $\phi_M$ = 4.75 eV | uestions):<br>${}^{2}k^{-1}$ , T=300 K, kT/q=0.026 V, $\epsilon_{0}$ =8.<br>.12 eV, $\mu_{n}$ =1300 cm <sup>2</sup> /V-s, $\mu_{p}$ (Si)=4 | .85×10 <sup>-14</sup> F/cm |

|                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                            |                            |

Answer should be very brief and to the point.

- Q1. What is the probability of finding of an electron at the conduction band  $[f(E_c).]$  of pure [2] Silicon at 20°C ? Ans:

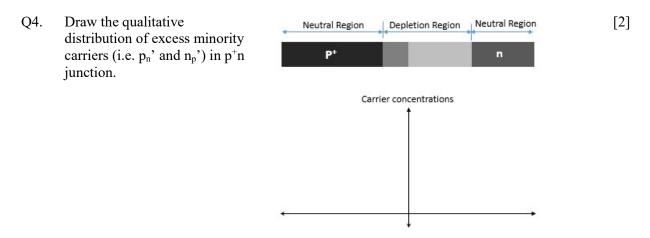

- Q2. Consider a  $P^+n$  junction, where  $N_D$  is tripled. If everything else remains same, how do the [2] parameters listed below change. Tick the correct answer.

- (a) Depletion capacitance: Increase / Decrease

- (b) Built-in potential: Increase / Decrease

- (c) Breakdown voltage: Increase / Decrease

- (d) Ohmic losses: Increase / Decrease

- Q3. For a Si p-n junction,  $N_A=N_D=10^{17}$  cm<sup>-3</sup>. Find the applied revise bias voltage when [2] maximum electric field will be 5×10<sup>5</sup> V/cm. (T = 300 k) Ans:

- Q5 Write the continuity equation for electron while electric filed is constant. Ans:

- Q6. What is preferred for less shift of the threshold voltage due to effect of body bias potential [1] (or body effect). Tick the correct answer.

- (a) High/ Low substrate doping (N<sub>A</sub>)

- (b) Thick/ Thin oxide thickness (tox)

- Q7. For a sharp subthreshold slope (small S), what will be the preferable combinations. Tick [2] the correct response:

- (a) High / Low channel doping,

- (b) Thick / Thin oxide thickness,

- (c) High / Low interface-trap density

- (d) High/ Low substrate bias voltage.

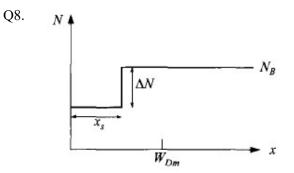

If the given non-uniform doping profile is used [1] instead of a uniform doping profile for a MOSFET, what will be change in depletion width and threshold voltage. Tick the correct response.

- (a) Depletion width will increase / decrease

- (b) Threshold voltage will increase /decrease

- Q9. Draw a schematic of a short channel MOSFET to indicate the charge sharing effect. [2] Ans:

- Q10. What is the reason behind the faster operation in SOI MOSFET as compared to the [2] conventional bulk MOSFET? Ans:

- Q11. An n-channel MOSFET having oxide thickness of 4 nm, substrate doping of 5×10<sup>16</sup> cm<sup>-3</sup>, [2] and flat band voltage of -1.1 V. Calculate the particular gate to source voltage (V<sub>gs</sub>) where immediate oxide breakdown can possible at the starting of strong inversion. (Breakdown strength of SiO<sub>2</sub> is 18 MV/cm). Ans:

[2]

- Q12. Consider an ideal MOS capacitor Ans: having n-type Si substrate. Draw the qualitative carrier (hole and electron) distribution profile under week inversion.

- Q13. Draw an energy band diagram of Ans:  $SiO_2/Si$  system to indicate the band offset of ~3.1 eV.

- Q14. Draw a schematic of floating body Ans: in a n-channel partially depleted (PD) SOI MOSFET. Clearly indicate the all the capacitance and pn junction diodes.

- Q15. Sketch and label the transfer Ans: characteristics ( $I_D$  vs  $V_{GS}$ ) of a n-channel **buried** device (MOSFET).

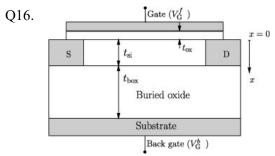

Q17. Consider 's' is the scaling factor. For, constant field scaling, write the appropriate scaled parameters. Example: Gate length (L): L/s Write the expressions of all three capacitances used [3] in threshold voltage expression of the given FD-SOI-MOSFET.

- Doping (N<sub>A</sub>):

- Propagation delay (τ):

- Power delay product (P. $\tau$ ):

- Subthreshold slope (S):

P.T.O.

[2]

[2]

[2]

[2]

[2]

Q18. Draw an energy band diagram of a short channel n-MOSFET to indicate the drain voltage [2] induced barrier lowering.

[2]

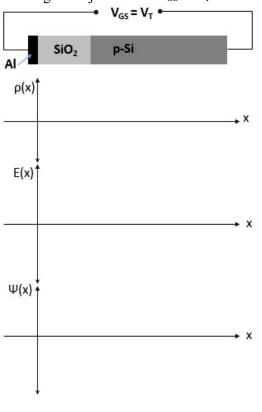

Q20. Draw the charge ( $\rho$ ), electric filed (E) and potential ( $\psi$ ) distribution pattern for the [3] following MOS junction at V<sub>GS</sub> = V<sub>T</sub>. Consider the MOS junction is ideal one.

-----End-----

## **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

COMPREHENSIVE EXAMINATION

Semester I: 2023-2024

## Part B: Open Book

MEL G631: Physics and Modelling of Microelectronic Devices

Date: 08/12/2022Maximum Marks: 40Maximum Time: 90 minutes

Given (Use, if not specified in the questions):  $q=1.6\times10^{-19}$  C,  $k=1.38\times10^{-23}$  m<sup>2</sup>kgs<sup>-2</sup>k<sup>-1</sup>, T=300 K, kT/q=0.026 V,  $\epsilon_0=8.85\times10^{-14}$  F/cm **Si:**  $\epsilon_r=11.9$ ,  $n_i=1.45\times10^{10}$  cm<sup>-3</sup>,  $E_g=1.12$  eV,  $\mu_n=1300$  cm<sup>2</sup>/V-s,  $\mu_p(Si)=480$  cm<sup>2</sup>/V-s,  $q\chi=4.05$  eV,  $N_C=2.8\times10^{19}$  cm<sup>-3</sup>,  $N_V=1.04\times10^{19}$  cm<sup>-3</sup>. **SiO**<sub>2</sub>:  $\epsilon_r=3.9$

Attempt all the questions.

## Q1.

(a) Sketch and label the energy band diagram of a Metal-Silicon (M-S) junction under thermal equilibrium at 300 K. Consider, metal work function 4.1 eV, donor doping in Silicon as  $5 \times 10^{16}$  cm<sup>-3</sup>. Comment on the type of the junction. [5]

(b) Given acceptor profile  $N_A(x)=N_0e^{-ax}$ . Sketch and label following quantities with respect to 'x'.

(i) Diffusion current  $(J_{pdiff})$  [2]

(ii) Drift current (J<sub>pdrift</sub>) [1]

(iii) Electric filed  $(E_x)$  [2]

**Q2.** An abrupt  $p^+n$  silicon junction (long base) having  $10^{-4}$  cm<sup>2</sup> cross section with following information

| p <sup>+</sup> side                                                          | n side                                                                        |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| $N_A = 10^{17} \text{ cm}^{-3}, \tau_n = 0.1  \mu\text{s}$                   | $N_D = 10^{15} \text{ cm}^{-3}, \tau_p = 10  \mu\text{s}$                     |

| $\mu_p = 200 \text{ cm}^2/\text{V-s}, \ \mu_n = 700 \text{ cm}^2/\text{V-s}$ | $\mu_n = 1300 \text{ cm}^2/\text{V-s}, \ \mu_p = 450 \text{ cm}^2/\text{V-s}$ |

At a particular bias, current is measured as 1 mA.

- (a) Find the applied bias voltage [5]

- (b) Find  $I_p$  hole current at  $x = x_n$  [2]

- (c) Also, find in (electron current) at  $x = x_n [1]$

- (d) Sketch the hole and electron current of the  $p^+n$  junction under forward bias. [2]

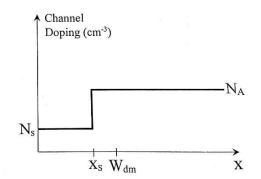

**Q3.** Consider an n-channel MOSFET with n<sup>+</sup> polysilicon gate. Gate oxide thickness is 7 nm, fixed oxide charge  $5 \times 10^{10}$  cm<sup>-2</sup> and p-type body has a step (non-uniform) doping (N<sub>A</sub>>>N<sub>S</sub>) as shown in the figure below. Write the threshold voltage expression considering the approximation N<sub>S</sub>  $\approx$  0 and find the value of X<sub>s</sub> and N<sub>A</sub> when threshold voltage is 0.3 V and corresponding surface potential ( $\Psi_{\rm S}=2\Psi_{\rm B}$ ) as 1 V. Also, calculate the maximum depletion width (W<sub>dm</sub>). **[10]**

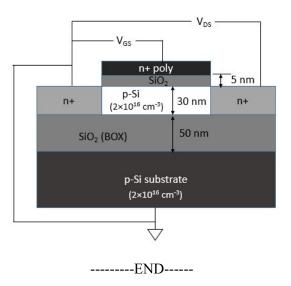

Q4. Consider interface charges  $Q_f/q=5\times10^{11}$  cm<sup>-2</sup> (applicable for front and back both the interfaces)

(a) Show the type of the device i.e. FD or PD SOI. [2]

(b) Find the back surface potential ( $\Psi_{sb}$ ). Also, comment on the condition of the back interface (i.e. accumulation, depletion or inversion). [4]

- (c) Find accurate front gate threshold voltage of the SOI MOSFET. [3]

- (d) Find body factor (n) of the device and estimate  $V_{DSAT}$  for applied  $V_{GS}=1$  V. [1]

(Hint: Consider the flat band voltage in the calculation)